전공 성과

- 전공 소식

- 전공 성과

[김태환 교수 연구실] 김태환 교수와 학부 연구생 3인 (하정원, 이원우, 고태훈)의 논문 회로 및 시스템 설계 분야 Flagship 저널에 (IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems) 게재 확정].

- 김지혜

- 2026-03-20

김태환 교수와 학부

연구생

하정원,

이원우,

고태훈

학생이

수행한

연구를

기반으로

작성한

논문이

회로

및

시스템

설계

분야의

명실

상부한

Flagship 저널 중

하나인

IEEE Transactions on Computer-Aided Design of Integrated

Circuits and Systems에 게재 확정되었다.

본

연구는

다른

연구

기관

과의

협업

없이

본

연구실

단독으로

진행하여

이룬

성과로,

본

연구실의

높은

연구

역량을

입증하고

있음.

논문의 제목은 “Softmex:

Lightweight Softmax Compute Engines Based on Exponentiation Units” 으로

AI 모델의 필수적인 연산인

소프트맥스를

계산하는

전용

회로

설계와

관련된

혁신적인

아이디어를

제안하고

있음.

번거로운

사전

정규화와

나눗셈

과정을

수학적

변형을

통해

없애고,

단순한

'지수

계산'

만으로

전체

연산을

처리하는

새로운

계산

알고리즘을

제안하고,

이를

기반으로

하는

고성능

저면적의

소프트맥스

엔진을

디지털

회로로

설계,

구현하여

성능을

평가하였으며,

BERT 모델을

기반으로

하는

GLUE Task를 기반으로 수치적인

성능을

검증하였음.

제안하는

소프트맥스

엔진은

기존

세계

최고

연구

결과

대비

4.4배

높은

면적

효율성을

달성하였음.

김태환 교수 연구실

(https://cas.kau.ac.kr) 에서는 효율적인 AI 가속기를

위한

Digital VLSI 시스템과 하드웨어를 고려한

AI 모델

최적화와

관련된

다양한

연구를

수행

중이며,

우수

학부

연구생과

대학원생을

상시

모집중임.

-

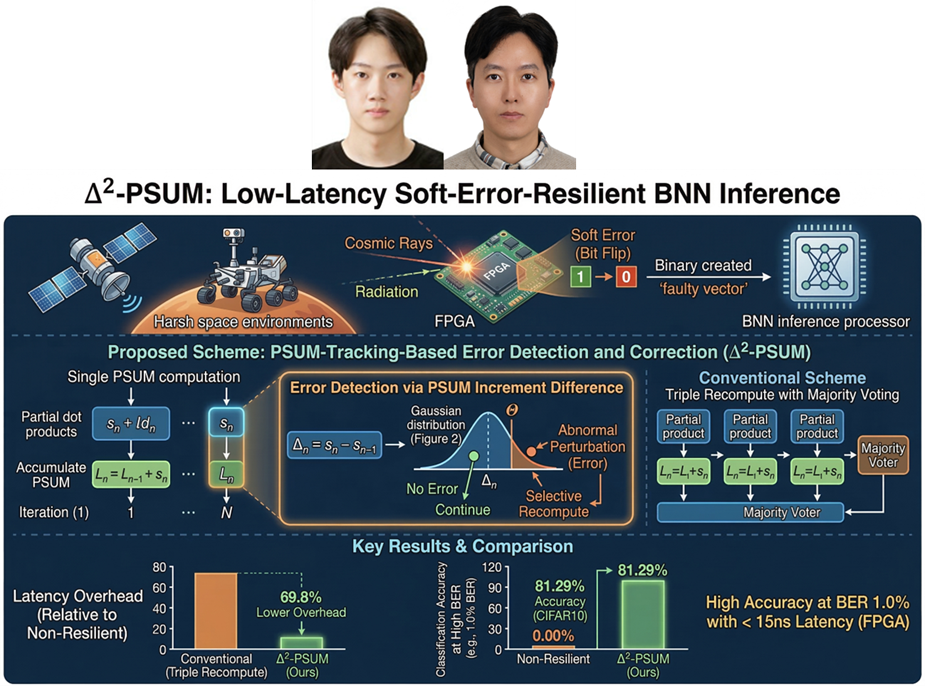

[김태환 교수 연구실] 김태환 교수 연구실의 석사 과정 정새벽 학생의 논문, FPGA 회로 및 시스템 설계 분야 우수 학술대회에 (IEEE Int’l Symp. Field-Programmable Custom Computing Machines) 발표 승인].

2026-03-20

김태환 교수와 석사 과정 정새벽 학생의 연구 논문이 FPGA 회로 및 시스템 설계 분야의 권위있는 학술 대회 중 하나인 IEEE Int’l Symp. Field-Programmable Custom Computing Machines (FCCM)에 발표 (Oral) 승인되었음. FCCM은 한국정보과학회에서 A급 우수 국제학술대회로 분류되어 있음. 본 연구는 다른 연구 기관 과의 협업 없이 본 연구실 단독으로 진행하여 이룬 성과로, 본 연구실의 높은 연구 역량을 입증하고 있음.

논문의 제목은 “Δ2-PSUM: A Low-Latency Soft-Error-Resilient Binary Neural Network Inference Processor”으로 본 논문은 우주 방사선 등 가혹한 환경에서 발생하는 소프트 에러에 대응하기 위해 고안된 효율적인 이진 신경망 추론 프로세서를 제안함. 해당 프로세서는 부분합 증가량에 급격한 변화가 발생할 때만 선택적으로 재연산을 수행하는 기법을 도입하여, 오류를 수정하면서도 불필요한 연산을 대폭 줄여 매우 짧은 지연 시간을 달성함. 28nm FPGA 하드웨어에서 2.41k LUT라는 아주 적은 자원만으로 구현되었으며, 단 14.57ns 만에 CIFAR10 이미지 하나를 분류할 수 있는 뛰어난 효율성을 보여줌. 결과적으로 1.0%의 높은 BER 환경에서도 정확도 하락을 최소화해 81.29%의 신뢰성 있는 분류 정확도를 유지함으로써, 제한된 하드웨어 자원 내에서 에러 복원력과 연산 효율성을 모두 성공적으로 입증함.

김태환 교수 연구실 (https://cas.kau.ac.kr) 에서는 효율적인 AI 가속기를 위한 Digital VLSI 시스템과 하드웨어를 고려한 AI 모델 최적화와 관련된 다양한 연구를 수행 중이며, 우수 학부 연구생과 대학원생을 상시 모집중임.

-

이효창 교수 연구팀, 2차원 반도체 접촉 공정 세계 최초 체계화… ACS Nano 부표지 논문 게재

2026-03-10

반도체시스템전공 이효창 교수 연구팀이 서울시립대학교 김태완 교수 연구팀과 공동으로 수행한 연구 논문이 세계적 권위의 나노과학 분야 학술지 ACS Nano(IF 16.1, JCR 기준 상위 6%)에 게재되며 부표지(Supplementary Cover) 논문으로 선정됐다.

이번 연구는 ‘Plasma Knowledge-Based Polymorphic Engineering for Two-Dimensional Semiconductor Contacts’라는 제목으로 발표됐으며, 차세대 반도체 소재로 주목받는 2차원 전이금속 칼코게나이드(2D TMD) 소자에서 성능 저하의 주요 원인으로 지적돼 온 높은 접촉저항 문제를 공정 기술 측면에서 해결할 수 있는 방법을 제시했다.

최근 반도체 소자의 초미세화가 진행되면서 기존 실리콘 기반 트랜지스터는 단채널 효과, 열 방출 증가, 전자 이동도 감소 등 여러 기술적 한계에 직면하고 있다. 이를 극복할 대안으로 원자 두께 수준의 2차원 반도체 소재가 주목받고 있지만, 금속 전극과 반도체 사이에서 발생하는 접촉저항 문제는 상용화를 가로막는 중요한 기술적 과제로 남아 있었다.

연구팀은 기존 플라즈마 공정이 경험적 조건 조정에 의존해 왔던 한계를 넘어, 플라즈마 이온 밀도와 자기 바이어스 전압 등 내부 물리량을 정량적으로 계측하고 이를 공정 제어에 활용하는 방식을 제안했다. 이를 바탕으로 이온 에너지 플럭스(ion energy flux, 플라즈마 이온이 물질 표면에 전달하는 에너지 흐름)를 정밀하게 제어하는 ‘플라즈마-지식기반 다형상(polymorphic) 공정’ 프레임워크를 세계 최초로 체계화했다.

이 기술을 통해 연구팀은 2차원 전이금속 칼코게나이드 반도체 소재인 MoTe₂(몰리브덴 텔루라이드)와 WS₂(텅스텐 디설파이드)에서 반도체 상(2H) 내부에 금속 상(1T′)을 선택적으로 형성하는 1T′/2H 다형상( polymorphic) 접합 계면을 형성했다. 이는 하나의 재료 내부에서 금속과 반도체 특성이 공존하도록 만드는 구조로, 금속 전극과 반도체 사이에서 형성되는 쇼트키 장벽(Schottky barrier, 전류 흐름을 방해하는 에너지 장벽)을 크게 낮춰 저저항 오믹 접촉을 구현할 수 있다.

또한 이 공정 전략이 2차원 전이금속 칼코게나이드 반도체 소재인 MoTe₂(몰리브덴 텔루라이드)와 WS₂(텅스텐 디설파이드)에도 동일하게 적용 가능함을 확인해, 특정 소재에 국한되지 않는 범용 2차원 반도체 접촉 공정 플랫폼으로 확장될 가능성을 보여줬다.

이효창 교수는 “이번 연구는 2차원 반도체 접촉저항의 난제를 공정-물리량 기반 제어라는 방식으로 해결한 사례로서, AI·우주·초저전력 반도체와 같은 차세대 응용 기술의 구현 시점을 앞당기는 데 의미가 있다”고 말했다.

논문 원문은 다음 링크에서 확인할 수 있다. https://pubs.acs.org/doi/abs/10.1021/acsnano.5c17260